310704

Roll No.

Total No of Pages: 3

https://www.btubikaner.com

## 310704

## B. Tech. III - Sem. (Main) Exam., February - 2021 Electronics & Communication Engineering 3EC4-04 Digital System Design Common ECE/EIC

Time: 3 Hours Maximum Marks: 120

## Instructions to Candidates:

- Part A: Short answer questions (up to 25 words)  $10 \times 2$  marks = 20 marks. All ten questions are compulsory.

- **Part B:** Analytical/Problem Solving questions (up to 100 words)  $5 \times 8$  marks = 40 marks. Candidates have to answer five questions out of seven.

- **Part C:** Descriptive/Analytical/Problem Solving questions  $4 \times 15$  marks = 60 marks. Candidates have to answer four questions out of six.

Schematic diagrams must be shown wherever necessary. Any data you feel missing may suitably be assumed and stated clearly. Units of quantities used/calculated must be stated clearly.

Use of following supporting materials is permitted during examination. (Mentioned in form No. 205)

1. <u>NIL</u>

2. NIL

## PART - A

| <b>7</b> 0.1 | Draw symbol and truth table of all Logic gates. Non            |   | [2]   |

|--------------|----------------------------------------------------------------|---|-------|

| $\int_{0.2}$ | What is Universal Logic Gate? Draw OR gate using NAND gate?    |   | [2]   |

| - /-         | How is function of multiplexer different from de-multiplexer.  |   | [2]   |

|              | Define Hold – time and propagation delay time in Flip – Flops. | * | [2]   |

|              | Write merit & demerits of ECL Logic family.                    |   | [2]   |

|              | Compare Series and Parallel Adders.                            |   | [2]   |

|              | What is difference between Synchronous and Ripple counter?     |   | [2]   |

| [310         |                                                                |   | [400] |

https://www.btubikaner.com

| nttps://www.btubikaner.com                                                                                  |              |  |  |

|-------------------------------------------------------------------------------------------------------------|--------------|--|--|

| Q.8 Write advantages and disadvantages of CMOS family.                                                      | [2]          |  |  |

| Q.9 Write briefly different modeling styles in VHDL.                                                        | [2]          |  |  |

| Q.10 What factors need to be optimized for a good VLSI design?                                              | [2]          |  |  |

| PART – B                                                                                                    |              |  |  |

| Q.1 Convert following number systems:                                                                       |              |  |  |

| (a) Decimal to 8421 BCD code – 114, 37.2                                                                    | [4]          |  |  |

| (b) Convert to Hexadecimal – (62.75)8                                                                       | [4]          |  |  |

| Q.2 Simply using K – Map, the following expression –/                                                       |              |  |  |

| (a) $f(A, B, C, D) = \sum (0, 3, 6, 7, 9, 13, 14, 15)$                                                      | [4]          |  |  |

| (b) $Y = \overline{A}BC + ABC + A\overline{B}\overline{C} + A\overline{B}C + ABC$                           | [4]          |  |  |

| Q.3 Draw logic diagram of a 8:1 multiplexer and explain its working.                                        | [8]          |  |  |

| Q.4 Write merits and demerits of various Logic families.                                                    | [8]          |  |  |

| Q.5 Briefly explain terms: Noise margin, Fan - in & fan - out, FPGA.                                        | [2×4=8]      |  |  |

| Q.6 Drawa state diagram and logic diagram of 4 - bit ring counter using D Flip                              | p – Flops or |  |  |

| JK Flip - Flop. https://www.btubikaner.com                                                                  | [8]          |  |  |

| Q.7 Why do we use VHDL? What is IC design flow? Explain briefly.                                            | [8]          |  |  |

| PART - C                                                                                                    |              |  |  |

| Q.1 (a) Using the Quine – McClusky method of tabular reduction minimize the function.                       |              |  |  |

| Q.1 (a) Using the Quine – Welclusky method of details $f(A, B, C, D) = \sum m(0, 2, 3, 6, 7, 8, 9, 10, 13)$ | [10]         |  |  |

| A = A = A = A = A = A = A = A = A = A =                                                                     | [5]          |  |  |

| O.2 (a) Design a 4 – bit Binary to Gray code converter, also draw logic diagram                             | m. [10]      |  |  |

|                                                                                                             | [5]          |  |  |

| (b) Implement using 8 ×1 Max the remarks $f(A, B, C, D) = \sum m(1, 3, 4, 11, 12, 13, 14, 15)$              |              |  |  |

|                                                                                                             | [5]          |  |  |

| (a) Convert J – K Flip – Flop into D and T Flip – Flop.                                                     | [5]          |  |  |

| (b) Design a Modulo – 10 counter using Flip – Flops.                                                        | [5]          |  |  |

| (c) Draw a ring counter using flip – flops and show state diagrams.                                         | 4.503        |  |  |

| [310704] Page 2 of 3                                                                                        | [400]        |  |  |

| [azororj                                                                                                    |              |  |  |

https://www.btubikaner.com

- Q.4 (a) With diagram explain working of -

- CMOS NOR gate with two inputs (i)

[5]

(ii) MOS NAND gate with two inputs

[5]

Briefly describe interfacing issues of various logic families.

[5]

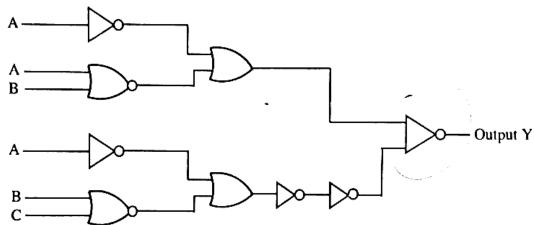

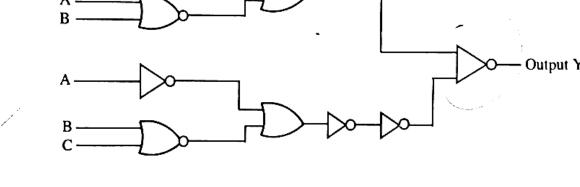

Using universal logic gates draw a logic gate diagrams to implement the function of the following logic diagram. [5]

- What are sequential logic circuits? How they are designed using various flip flop? Show the designing of a synchronous counter to count up and down with facility to skip any one number in counting sequence. [10]

- $[3 \times 5 = 15]$

https://www.btubikaner.com

- Q.6 Describe the terms in context to VLSI design (any three)-

- FSM and HDL (i)

- (ii) Data types and objects

- (iii) VHDL constructs and codes

- (iv) Behavioural and structural modeling

https://www.btubikaner.com Whatsapp @ 9300930012 Send your old paper & get 10/-अपने पुराने पेपर्स भेजे और 10 रुपये पार्य, Paytm or Google Pay रा

[310704]

Page 3 of 3

[400]

١.

https://www.btubikaner.com